PSoCカスタムコンポーネントでFIFOを実装する

これまではデータパスのA0レジスタの値を扱ってきましたが、データパスにはFIFOバッファが備わっており、これらに値を蓄積することで滞りないデータの送受信ができます。特に、連続的なメモリー転送を行うDMAを利用するのであればFIFOの実装は不可欠です。

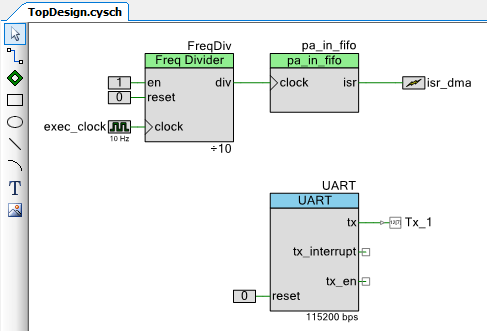

並列入力のサンプルを前回に作ったので、これをFIFOバッファに対応させてみましょう。

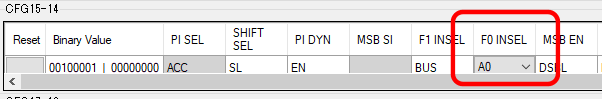

FIFOを制御するにはF0/F1レジスタを使用します。データパス設定ツールでVerilogファイルを開いたら、「F0 INSEL」の値を「A0」に変更しましょう。これでA0レジスタがF0レジスタにコピーされるようになります。

F0レジスタへの挿入は「f0_load」で指定したレジスタがHighのときに、クロックごとに実行されます。FIFOバッファにデータ存在するとき、「f0_bus_stat」に指定したレジスタの値がHighになるので、これを出力ワイヤに紐付けることで、いつデータを取得すればよいかを知ることができます。

fifo.v

`include "cypress.v"

module pa_in_fifo (

input clock,

output isr

);

localparam RG_IDLE = 3'b000;

localparam RG_COPY = 3'b001;

reg [2:0]rg_state;

reg[7:0] pa_in_reg;

reg[1:0] val_type;

reg load_fifo;

always @(posedge clock)

begin

case(rg_state)

RG_IDLE:

begin

load_fifo = 1'b0;

rg_state = RG_COPY;

end

RG_COPY:

begin

case(val_type)

2'b00:

begin

pa_in_reg = 8'b11111111;

end

2'b01:

begin

pa_in_reg = 8'b11110000;

end

2'b10:

begin

pa_in_reg = 8'b11001100;

end

2'b11:

begin

pa_in_reg = 8'b10101010;

end

endcase

val_type = val_type + 1'b1;

load_fifo = 1'b1;

rg_state = RG_IDLE;

end

endcase

end

cy_psoc3_dp #(.cy_dpconfig(

{

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM0:IDLE*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC__ALU, `CS_A1_SRC_NONE,

`CS_FEEDBACK_ENBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM1:COPY PI to A0*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC__ALU, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM2:*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM3:*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM4:*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM5:*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM6:*/

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM7:*/

8'hFF, 8'h00, /*CFG9:*/

8'hFF, 8'hFF, /*CFG11-10:*/

`SC_CMPB_A1_D1, `SC_CMPA_A1_D1, `SC_CI_B_ARITH,

`SC_CI_A_ARITH, `SC_C1_MASK_DSBL, `SC_C0_MASK_DSBL,

`SC_A_MASK_DSBL, `SC_DEF_SI_0, `SC_SI_B_DEFSI,

`SC_SI_A_DEFSI, /*CFG13-12:*/

`SC_A0_SRC_ACC, `SC_SHIFT_SL, `SC_PI_DYN_EN,

1'h0, `SC_FIFO1_BUS, `SC_FIFO0__A0,

`SC_MSB_DSBL, `SC_MSB_BIT0, `SC_MSB_NOCHN,

`SC_FB_NOCHN, `SC_CMP1_NOCHN,

`SC_CMP0_NOCHN, /*CFG15-14:*/

10'h00, `SC_FIFO_CLK__DP,`SC_FIFO_CAP_AX,

`SC_FIFO_LEVEL,`SC_FIFO__SYNC,`SC_EXTCRC_DSBL,

`SC_WRK16CAT_DSBL /*CFG17-16:*/

}

)) dp(

.clk(clock),

.cs_addr(rg_state),

.f0_load(load_fifo),

.f0_bus_stat(isr),

.pi(pa_in_reg)

);

endmodule

あとは、取得元レジスタをA0からF0に置き換えれば完成です。

fifo_api.h

#ifndef __`$INSTANCE_NAME`_H__

#define __`$INSTANCE_NAME`_H__

#define `$INSTANCE_NAME`_GetValue() CY_GET_REG8(`$INSTANCE_NAME`_dp__F0_REG)

#endif

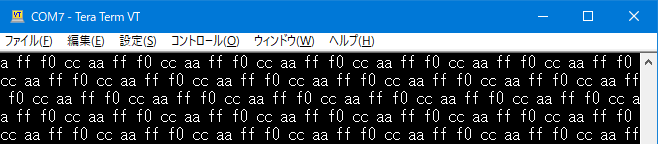

main.c

#include "project.h"

#include <stdio.h>

CY_ISR(OnIntrupptPaIn)

{

char str[10];

sprintf(str, "%x ", pa_in_fifo_GetValue());

UART_PutString(str);

}

int main(void)

{

CyGlobalIntEnable;

isr_dma_StartEx(OnIntrupptPaIn);

UART_Start();

for(;;)

{

}

}

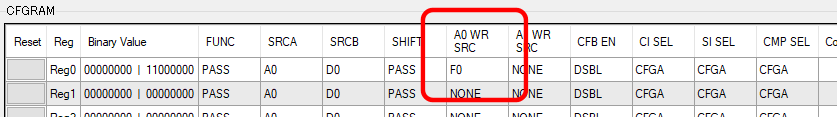

また、

並列出力サンプル(7セグドライバー)をFIFOに対応させるには、データパス設定ツールで「A0 WR SRC」の値を「F0」にすれば演算結果をF0レジスタに出力されるので、あとはAPIの参照先レジスタを「

CY_SET_REG8(`$INSTANCE_NAME`_dp__F0_REG, v)」と変更するだけです。

fifo_out.v

`include "cypress.v"

module pa_out (

input clock,

output[7:0] led_out

);

cy_psoc3_dp #(.cy_dpconfig(

{

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC___F0, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM0: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM1: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM2: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM3: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM4: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM5: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM6: */

`CS_ALU_OP_PASS, `CS_SRCA_A0, `CS_SRCB_D0,

`CS_SHFT_OP_PASS, `CS_A0_SRC_NONE, `CS_A1_SRC_NONE,

`CS_FEEDBACK_DSBL, `CS_CI_SEL_CFGA, `CS_SI_SEL_CFGA,

`CS_CMP_SEL_CFGA, /*CFGRAM7: */

8'hFF, 8'h00, /*CFG9: */

8'hFF, 8'hFF, /*CFG11-10: */

`SC_CMPB_A1_D1, `SC_CMPA_A1_D1, `SC_CI_B_ARITH,

`SC_CI_A_ARITH, `SC_C1_MASK_DSBL, `SC_C0_MASK_DSBL,

`SC_A_MASK_DSBL, `SC_DEF_SI_0, `SC_SI_B_DEFSI,

`SC_SI_A_DEFSI, /*CFG13-12: */

`SC_A0_SRC_ACC, `SC_SHIFT_SL, `SC_PI_DYN_DS,

1'h0, `SC_FIFO1_BUS, `SC_FIFO0_BUS,

`SC_MSB_DSBL, `SC_MSB_BIT0, `SC_MSB_NOCHN,

`SC_FB_NOCHN, `SC_CMP1_NOCHN,

`SC_CMP0_NOCHN, /*CFG15-14: */

10'h00, `SC_FIFO_CLK__DP,`SC_FIFO_CAP_AX,

`SC_FIFO_LEVEL,`SC_FIFO__SYNC,`SC_EXTCRC_DSBL,

`SC_WRK16CAT_DSBL /*CFG17-16: */

}

)) dp(

.clk(clock),

.cs_addr(3'b000),

.po(led_out)

);

endmodule

2019/06/17